# 2QD0435T17-C-xx Gate Driver Core

#### **Features**

#### RoHS COMPLIANT

- Dual-channel IGBT gate driver core

- Blocking voltage up to 1700V

- Peak current ±35A, 4W output power per channel

- Up to 5000V isolation voltage

- Direct/half-bridge mode available

- Primary/secondary side undervoltage lockout

- IGBT short-circuit protection integrated

- · Advanced active clamping integrated

| KEY PARAMETERS       |             |  |  |  |

|----------------------|-------------|--|--|--|

| Vcc                  | 15V         |  |  |  |

| V <sub>G</sub>       | +15V, -10V  |  |  |  |

| P, MAX               | 4W          |  |  |  |

| I <sub>G</sub> , MAX | ±35A        |  |  |  |

| fs, MAX              | 100kHz      |  |  |  |

| T <sub>A</sub>       | -40°C ~85°C |  |  |  |

| Isolation Voltage    | 5000Vac     |  |  |  |

#### Description

2QD0435T17-C-xx is a high power, dual-channel compact gate driver core designed for high reliability applications based on the ASIC chipset developed by Bronze Technologies.

2QD0435T17-C-xx can be used for IGBT modules with a blocking voltage up to 1700V. It can be applied to various topologies by adding proper peripheral circuitry.

## **Typical Applications**

- Engergy storage converters

- Wind power converters

- PV inverters

- Motor Drives

- SVG

- APF

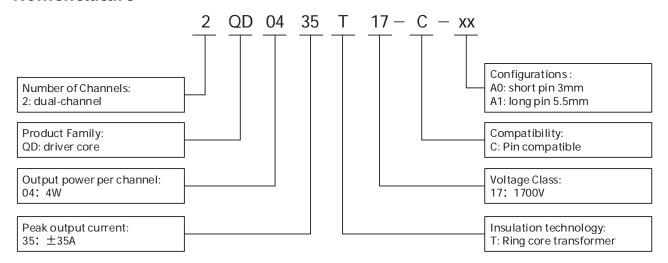

#### **Nomenclature**

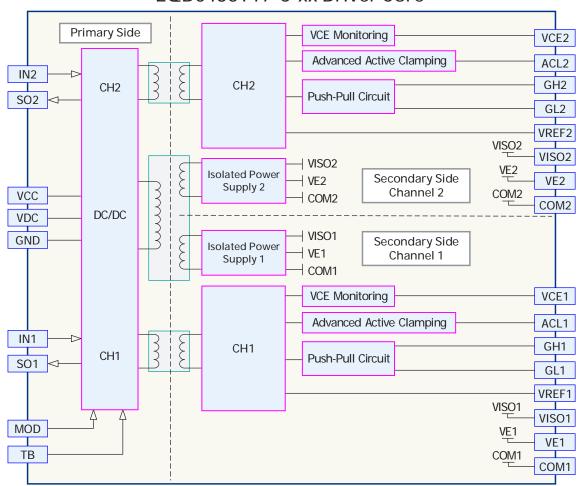

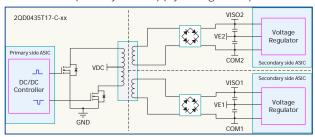

## **Block Diagram Of Driver Core**

#### 2QD0435T17-C-xx Driver Core

Figure 1. Block diagram of 2QD0435T17-C-xx

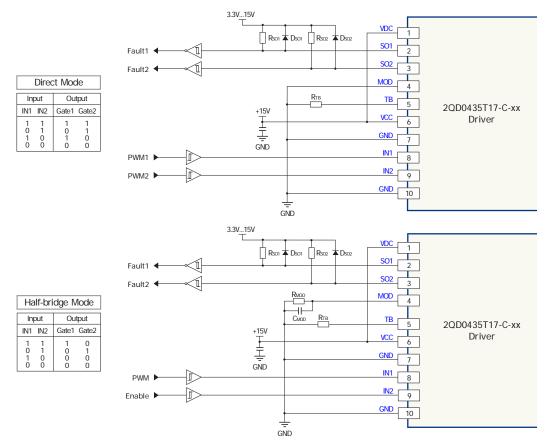

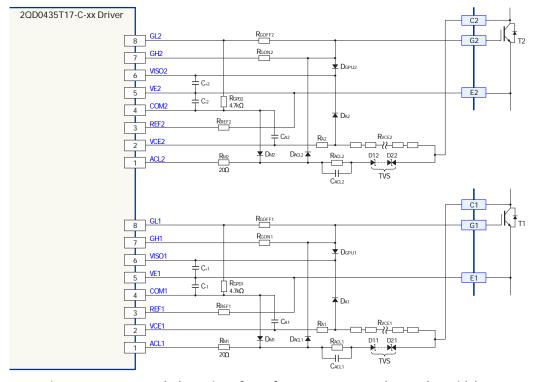

## **Recommended Circuitry**

Figure 2. Recommended user interface of 2QD0435T17-C-xx (Primary Side)

Figure 3. Recommended user interface of 2QD0435T17-C-xx (Secondary side)

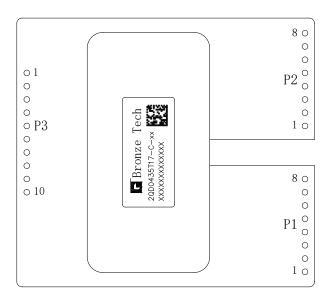

## **Pin Designation**

#### P1 Terminal

| Pin | Symbol                                                                         | Description                                           |  |

|-----|--------------------------------------------------------------------------------|-------------------------------------------------------|--|

| 1   | ACL1                                                                           | Advanced Active Clamping feedback channel 1 1)        |  |

| 2   | VCE1                                                                           | VCE sense channel 1 <sup>2)</sup>                     |  |

| 3   | 3 REF1 Set V <sub>CE</sub> detection threshold voltage channel 1 <sup>3)</sup> |                                                       |  |

| 4   | COM1                                                                           | COM1 Negative secondary side power supply channel 14) |  |

| 5   | VE1 Emitter channel 1 5)                                                       |                                                       |  |

| 6   | VISO1                                                                          | Positive secondary side power supply channel 1 6)     |  |

| 7   | GH1                                                                            | Gate high channel 1, gate ON output 7)                |  |

| 8   | GL1                                                                            | Gate low channel 1, gate OFF output 8)                |  |

#### P2 Terminal

| Pin | n Symbol Description                                                 |                                                                 |  |

|-----|----------------------------------------------------------------------|-----------------------------------------------------------------|--|

| 1   | ACL2                                                                 | Advanced Active Clamping feedback channel 2 1)                  |  |

| 2   | VCE2                                                                 | VCE sense channel 2 <sup>2)</sup>                               |  |

| 3   | 3 REF2 Set VCE detection threshold channel 2 <sup>3)</sup>           |                                                                 |  |

| 4   | COM2                                                                 | 12 Negative secondary side power supply channel 2 <sup>4)</sup> |  |

| 5   | VE2                                                                  | VE2 Emitter channel 2 <sup>5)</sup>                             |  |

| 6   | 6 VISO2 Positive secondary side power supply channel 2 <sup>6)</sup> |                                                                 |  |

| 7   | GH2 Gate high channel 2, gate ON output <sup>7)</sup>                |                                                                 |  |

| 8   | GL2                                                                  | Gate low channel 2, gate OFF output 8)                          |  |

Note: 1) Left open if unused. For the detailed configuration, see the section "Active Clamping".

- 2) The desaturation detection pin of the driver. For details, see the section "IGBT Short-Circuit Protection".

- 3) Threshold voltage setting pin for the internal desaturation detection comparator of the driver. For details, see the section "IGBT Short-Circuit Protection".

- 4) Driver negative supply. Extra blocking capacitors can be connected externally.

- 5) Connected to blocking capacitor and emitter of the power device.

- 6) Driver positive supply. Extra blocking capacitors can be connected externally.

- 7) Gate high pin is connected to the external turn-on resistor  $R_{GONx}$ . It is pulled to VISOx for ON state and becomes high impedance for OFF state .

- 8) Gate low pin is connected to the external turn-off resistor  $R_{GOFFx}$ . It is pulled to COMx for OFF state and becomes high impedance for ON state.

#### P3 Terminal

| Pin | Symbol | Description                              | Pin | Symbol | Description                      |

|-----|--------|------------------------------------------|-----|--------|----------------------------------|

| 1   | VDC    | 15V for DC/DC converter 1)               | 6   | VCC    | 15V for primary side electronics |

| 2   | SO1    | Status output channel 1                  | 7   | GND    | Ground                           |

| 3   | SO2    | Status output channel 2                  | 8   | IN1    | Signal input channel 1           |

| 4   | MOD    | Mode selection (direct/half-bridge mode) | 9   | IN2    | Signal input channel 2           |

| 5   | ТВ     | Set blocking time 4)                     | 10  | GND    | Ground                           |

Note: 1) A stable 15V DC power supply is recommended. Be sure to have enough blocking capacitors to avoid voltage dips.

Figure 4. 2QD0435T17-C-xx pin layout

## **Specifications**

#### **Absolute Maximum Ratings**

| PARAMETER                                            | REMARKS                          | MIN | MAX  | UNIT |

|------------------------------------------------------|----------------------------------|-----|------|------|

| Supply voltage V <sub>CC</sub> , V <sub>DC</sub>     | VCC, VDC to GND                  | 0   | 16   | V    |

| Logic input and output voltages                      | Primary side, to GND             | 0   | VCC  | V    |

| SOx current                                          | Failure condition, total current |     | 20   | mA   |

| Output power per channel                             | Operating termperature ≤ 85° C   |     | 4    | W    |

| Gate peak current <sup>1)</sup>                      |                                  | -35 | 35   | А    |

| External gate resistance                             | Turn-on and turn off             | 0.5 |      | Ω    |

| Operating voltage                                    |                                  |     | 1700 | V    |

| Average supply current I <sub>DC</sub> <sup>2)</sup> |                                  |     | 620  | mA   |

| Switching frequency                                  |                                  |     | 100  | kHz  |

| Operating temperature T <sub>A</sub>                 |                                  | -40 | 85   | °C.  |

| Storage temperature T <sub>S</sub>                   |                                  | -40 | 85   |      |

Note: 1. It is an absolute value and only valid for short pulses.

#### Power supply and monitoring

Operating temperature  $T_A=25^{\circ}$  C,  $V_{CC}=V_{DC}=15V$ , unless otherwise specified, tested along with the recommended interface circuitry.

| PARAM                                            | ETER                                   | TEST CONDITONS                                                    | MIN   | TYP  | MAX  | UNIT |

|--------------------------------------------------|----------------------------------------|-------------------------------------------------------------------|-------|------|------|------|

| Supply voltage V <sub>CC</sub> , V <sub>DC</sub> |                                        | VCC, VDC to GND, recommended value                                | 14.5  | 15   | 15.5 | V    |

| Supply current Icc                               |                                        | No load, f <sub>SW</sub> =0Hz                                     |       | 11   |      |      |

|                                                  |                                        | No load, f <sub>SW</sub> =5kHz, 50% duty cycle                    |       | 49   |      |      |

| Supply current loc                               | $R_{GON}=1\Omega$ , $R_{GOFF}=1\Omega$ | No load, f <sub>SW</sub> =10kHz, 50% duty cycle                   |       | 53   |      | mA   |

| Зарріў сапені івс                                | 11001 111,110011 111                   | Load capacitance 100nF,<br>f <sub>SW</sub> =10kHz, 50% duty cycle |       | 147  |      |      |

| Secondary-side full voltage V <sub>CCO</sub>     |                                        | VISOx to COMx, no load                                            | 24    | 25   | 26   |      |

| Secondary-side positive                          | voltage V+                             | VISOx to VEx, no load                                             | 14.5  | 15   | 15.5 | V    |

| Secondary-side negative                          | voltage V-                             | COMx to VEx, no load                                              | -10.5 | -10  | -9.5 |      |

| Primary side supply                              | Set fault V <sub>CCUV+</sub>           | WGG GND                                                           |       | 12.5 | 13   |      |

| UVLO threshold                                   | Clear fault Vccuvr+                    | VCC-GND                                                           | 13    | 13.5 | 14   |      |

| Voltage <sup>1)</sup> Monitoring hysteresis      |                                        |                                                                   |       | 1    |      |      |

| Secondary side positive supply UVLO threshold    | Set fault V <sub>UV+</sub>             | VICO. VI.                                                         | 11.5  | 12   | 12.5 | V    |

|                                                  | Clear fault V <sub>UVR+</sub>          | - VISOx-VEx                                                       |       | 12.5 | 13   |      |

| voltage 1)                                       | Monitoring hysteresis                  |                                                                   |       | 0.5  |      |      |

<sup>2.</sup> The average current may exceed the specified maximum value during transient (e.g. power supply start up). This short overload is allowed as long as the temperature rise after the transient does not exceed the thermal limitation.

#### (Continued)

| Secondary side negative        | Set fault V <sub>UV-</sub>     | VEx-COMx -                     | 4 | 4.4 | 5 |   |

|--------------------------------|--------------------------------|--------------------------------|---|-----|---|---|

| supply UVLO threshold          | Clear fault V <sub>UVR</sub> - |                                | 4 | 4.5 | 5 | V |

| voltage 1)                     | Monitoring hysteresis          |                                |   | 0.1 |   |   |

| Note: 1. See the section "Powe | r Supply and Monitoring" fo    | or timing diagram of the UVLO. |   |     |   |   |

#### **Logic Input and Output**

Operating temperature T<sub>A</sub>=25° C, V<sub>CC</sub>=V<sub>DC</sub>=15V, unless otherwise specified, tested along with the recommended interface circuitry.

| PARAMETER                                                    |                                     | TEST CONDITIONS                          | MIN | TYP | MAX | UNIT |

|--------------------------------------------------------------|-------------------------------------|------------------------------------------|-----|-----|-----|------|

| Input bias current I <sub>IN</sub>                           |                                     | $V_{IN} > 3V$                            |     | 180 |     | μΑ   |

| IN1, IN2                                                     | Turn-on threshold VINH              |                                          |     | 2.4 |     | \/   |

| Input voltage V <sub>IN</sub>                                | Turn-off threshold V <sub>INL</sub> |                                          |     | 1.6 |     | V    |

| Mada calactica register 1)                                   | Direct mode                         | MOD shorted to GND                       |     | 0   |     |      |

| Mode selection resistor 1)                                   | Half-bridge mode                    | MOD connected to GND via a resistor      | 72  | 150 | 182 | kΩ   |

| Blocking time setting resistor R <sub>TB</sub> <sup>2)</sup> |                                     |                                          | 75  |     | 185 |      |

| SO output voltage V <sub>SO</sub> <sup>3)</sup>              | Normal state                        | R <sub>SOx</sub> =4.7kΩ pulled up to VCC |     | 15  |     | \/   |

|                                                              | Blocking state                      | I <sub>SOx</sub> < 20mA                  |     |     | 0.7 | V    |

Note: 1. Mode selection and dead time configuration resistor. For details, see the section "Transmission Logic and Mode Selection".

- 2. The Blocking time configuration resistor. For details, see the section "Blocking Time Setting".

- 3. SOx ouputs have open-drain transistors, users need to add the pull-up resistor  $R_{SOx}$  externally. For more details see the section "Status Output Signal".

#### **Gate Drive Output**

Operating temperature  $T_A=25^{\circ}$  C,  $V_{CC}=V_{DC}=15V$ , unless otherwise specified, tested along with the recommended interface circuitry.

| PARAMETER                             |                                         | TEST CONDITIONS                              | MIN | TYP  | MAX | UNIT |

|---------------------------------------|-----------------------------------------|----------------------------------------------|-----|------|-----|------|

|                                       | ON-State, V <sub>GHx</sub> , GHx to Ex  | No load                                      |     | 15   |     |      |

| Output voltage                        | OFF-State, V <sub>GLx</sub> , GLx to Ex | No load                                      |     | -10  |     | V    |

|                                       |                                         | Output power 4W                              |     | -9.5 |     |      |

| Cata peak current la                  | Source current                          | $R_{GON}=0.5\Omega$ , $R_{GOFF}=0.5\Omega$ , |     |      | 35  | Α    |

| Gate peak current I <sub>G peak</sub> | Sink current                            | load capacitance 2.47uF                      | -35 |      |     | A    |

| Blocking capacitance for V+ 1)        |                                         | VISOx to VEx                                 |     | 9.4  |     |      |

| Blocking capacitance for              | V- 1)                                   | COMx to VEx                                  |     | 9.4  | ·   | μF   |

Note: 1. External blocking capacitors are required to be placed between VISOx and VEx as well as between VEx and COMx for gate charges above  $3\mu$ C. Ceramic capacitors are recommended. A minimum external blocking capacitance of  $3\mu$ F is recommended for every  $1\mu$ C of gate charge beyond  $3\mu$ C. Insufficient external blocking capacitance may lead to reduced driver efficiency and thermal overload.

#### **Short Circut Protection**

Operating temperature  $T_A=25^{\circ}$  C,  $V_{CC}=V_{DC}=15V$ , unless otherwise specified, tested along with the recommended interface circuitry.

| PARAMETER                                             | TEST CONDITIONS                                                       | MIN TYP M | AX UNI |

|-------------------------------------------------------|-----------------------------------------------------------------------|-----------|--------|

| Current through pin REFx (internal current source)    | R <sub>REF</sub> <70kΩ                                                | 150       | μΑ     |

| Blocking time t <sub>B</sub> 1)                       | R <sub>TB</sub> =150kΩ                                                |           | ms     |

|                                                       | TB shorted to ground                                                  | 10        | μs     |

| Transmission delay of fault state t <sub>SO 2</sub> ) | Secondary-side short-circuit protection action to fault status output | 600       | ns     |

Note: 1. For other blocking time configurations, see the section "Blocking Time Setting".

#### **Timing Characteristics**

Operating temperature T<sub>A</sub>=25° C, V<sub>CC</sub>=V<sub>DC</sub>=15V, unless otherwise specified, tested along with the recommended interface circuitry.

| PARAM                                                     | IETER                              | TEST CONDITIONS                                  | MIN | TYP | MAX | UNIT    |

|-----------------------------------------------------------|------------------------------------|--------------------------------------------------|-----|-----|-----|---------|

| Dropagation dalay 1) 3)                                   | Turn-on delay t <sub>d(on)</sub>   | MOD pin shorted to GND                           |     | 215 |     |         |

| Propagation delay 1) 3)                                   | Turn-off delay t <sub>d(off)</sub> | $R_{GON}=1\Omega$ , $R_{GOFF}=1\Omega$ , no load |     | 230 |     |         |

| Jitter of turn-on delay                                   |                                    |                                                  |     | ±5  |     | 200     |

| Jitter of turn-off delay  Output rise time $t_r^{(2)/3)}$ |                                    | D -10 D -10 m land                               |     | ±5  |     | ns<br>_ |

|                                                           |                                    | $R_{GON}=1\Omega$ , $R_{GOFF}=1\Omega$ , no load | 32  |     |     |         |

| Output fall time t <sub>f</sub> <sup>2) 3)</sup>          |                                    |                                                  | 32  |     |     |         |

| Dead time DT <sup>4)</sup>                                |                                    |                                                  |     | 3   |     | μs      |

| Jitter of dead time                                       |                                    | Half-bridge mode, R <sub>MOD</sub> =150kΩ        |     | ±50 |     | ns      |

Note: 1. The delay time is measured between 50% of the input signal and 10% (90%) voltage swing of  $V_{GHx}$  ( $V_{GLx}$ ). The delay time is independent of the output load.

- 2. Output rise (fall) time is measured at GH (GL) at the driver side of the gate resistor  $R_{GONx}(R_{GOFFx})$  between the 10% and 90% of the nominal voltage swing. The time constant of the output load capacitance in conjunction with the present gate resistors leads to an additional delay at the load side of the gate resistors.

- 3. The voltage swing is the diffrerence between the output voltage at ON and OFF state on the GH or GL pins, referred to Ex.

- 4. For dead time configuration see section "Transmission Logic and Mode Selection / Half-Bridge Mode".

<sup>2.</sup> Propagation delay time is from the secondary-side protection action to the primary-side SOx pin pulled down.

#### **Electrical Isolation**

Operating temperature T<sub>A</sub>=25° C, unless otherwise specified, tested along with the standard peripheral circuitry.

| PARAMI                                                                             | VALUE                       | UNIT |    |  |  |

|------------------------------------------------------------------------------------|-----------------------------|------|----|--|--|

| location Voltage (FOUT 10 DMC value)                                               | Primary to Secondary side   | 5000 | V  |  |  |

| Isolation Voltage (50Hz, 1s, RMS value)                                            | Secondary to Secondary side | 4000 | V  |  |  |

| Primary to secondary side 1)                                                       | Coupling capacitance        | 27   | pF |  |  |

|                                                                                    | Clearance distance          | 16.5 | mm |  |  |

|                                                                                    | Creepage distance           | 16.5 | mm |  |  |

| Cocondary to secondary (side 1)                                                    | Clearance distance          | 6.3  | mm |  |  |

| Secondary to secondary side 1)                                                     | Creepage distance           | 13   | mm |  |  |

| Note: 1. Clearance and creepage distances are designed according to IEC 61800-5-1. |                             |      |    |  |  |

#### **EMC**

Ambient temperature T<sub>A</sub>=25° C, tested along with the standard peripheral circuity.

| PARAMETER                                                   |                   | VALUE | UNIT |

|-------------------------------------------------------------|-------------------|-------|------|

| ESD immunity (IEC 61000-4-2)                                | Contact discharge | ±4    |      |

|                                                             | Air discharge     | ±8    | kV   |

| Electrical fast transient/burst immunity 1) (IEC 61000-4-4) |                   | ±4    |      |

| Impulse magnetic field immunity (IEC 61000-4-9)             |                   | ±2000 | A/m  |

| Note: 1. Tested on power ports.                             |                   |       |      |

## **Ordering Information**

| Part Number     | IGBT Voltage | Pin Length | Conformal Coating |

|-----------------|--------------|------------|-------------------|

| 2QD0435T17-C-A0 | < 1700V      | 3mm        | Yes               |

| 2QD0435T17-C-A1 | < 1700V      | 5.5mm      | Yes               |

### **Function Description**

#### **Power Supply And Monitoring**

The DC/DC circuitry of the driver provides galvanic isolation between external power supply and gate driving circuit. Supply monitoring circuitry is deployed for the primary-side and two secondary-sides of the drive for undervoltage lockout.

Note: A stable primary side supply voltage is required.

Figure 5. Power supply circuitry

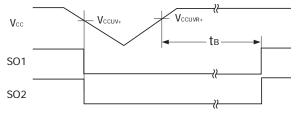

#### **Primary Supply Monitoring:**

The supply voltage Vcc is monitored on the primary-side for undervoltage lockout (UVLO). When Vcc drops to the UVLO threshold Vccuv+, UVLO is triggered, two secondary-side outputs are locked in off state and keep the IGBT off. Meanwhile, the fault signals SO1 and SO2 are pulled down.

When  $V_{CC}$  returns to the UVLO clear fault threshold  $V_{CCUVR+}$ , the driver continues to maintain the lockout state for a period  $t_B$ , then exit the lockout state and pulls up fault signals SOx.

Figure 6. Primary-side UVLO logic

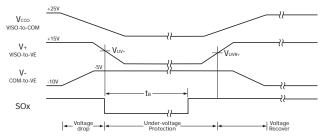

#### Secondary Side Supply Monitoring:

The secondary power supply voltage is also monitored to ensure a safe IGBT switching. To demonstrate the behavior of the secondary side UVLO, a scenario is considered in below where the primary side supply voltage Vcc decreases from the nominal value towards zero:

- 1) At first the positive voltage V+ (VISO to VE) is held constant on the nominal value, while the negative voltage V- (COM to VE) deviates from the nominal value towards zero along with the decreasing Vcc.

- 2) As soon as V- reaches -5V, V- is held constant and V+

starts to fall towards zero if VCC further collapses.

- 3) When V+ reaches the set fault threshold  $V_{UV+}$ , UVLO protection is initiated. The IGBT is turned off and held in off state, meanwhile a set fault signal is transmitted to the primary side and asserts SOx pin immediately.

- 4) The counting of  $t_B$  starts when a UV fault is detected. This is different from the primary side supply voltage monitoring, where the counting of  $t_B$  starts after UV fault is cleared. If a new fault is detected before  $t_B$  of the previous fault elapses,  $t_B$  is recounted from the new fault.

- 5) When  $V_{CC}$  rises again, the driver firstly restores V+.

- 6) If V+ further increases and reaches its nominal value, V+ is held constant and V- starts to recover towards its nominal value.

Figure 7. Secondary-side UVLO logic

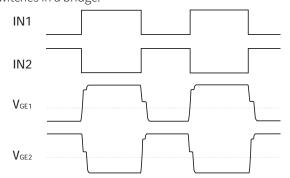

#### **Transmission Logic and Mode Selection**

The driver can operate in direct or half-bridge mode. Operation mode of the driver can be selected by configuring the connection of the MOD pin.

#### Direct Mode:

If the MOD pin is shorted to ground, direct mode is selected. In direct mode, the two channels are independent. Input IN1 determines the output of Channel 1, while input IN2 determines that of Channel 2. A logic high turns on the corresponding IGBT, while a logic low turns it off.

Note: In direct mode, make sure to add a proper dead time in the input signals to avoid shoot-through of the two switches in a bridge.

Figure 8. Transmission logic in direct mode

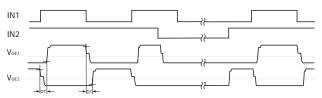

#### Half-Bridge Mode:

If the MOD pin is connected to ground via a resistor, the driver operates in half-bridge mode. In this mode, the IN1 serves as PWM signal and the IN2 as enabling signal.

When IN2 is low, both channels are locked in off state. If IN2 is high, both channels are enabled. The gate output signals of both channels are determined by IN1. At the transition of IN1 from low to high, the gate signal of Channel 2 is turned off immediately. After the dead time DT elapses, the gate signal of Channel 1 is turned on. At the transition of IN1 from high to low, the gate signal of Channel 1 is turned off immediately. After the dead time DT elapses, the gate signal of Channel 2 is turned on.

The dead time is set by an external resistor  $R_{\text{MOD}}$  connected between MOD pin and GND. The following formula defines the relationship between  $R_{\text{MOD}}$  and the dead time DT:

# $R_{\text{MOD}} \ [k\Omega] = 30.9 \cdot \text{DT}[\mu\text{s}] + 55.9$ $0.5\mu\text{s} < \text{DT} < 4.1\mu\text{s}, 72k\Omega < R_{\text{MOD}} < 182k\Omega$

When  $R_{MOD}=150k\Omega$ , the dead time DT is around 3.0us.

Figure 9. Transmission logic in half-bridge mode

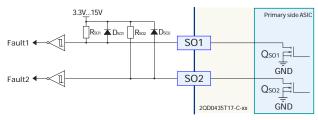

#### **Status Output Signal**

When no fault is detected, Q<sub>SOx</sub> keeps off, the outputs SOx have high impedance. When a fault is detected, the corresponding SOx is pulled down to ground.

It is recommended to mount external pull-up resistors as demonstrated in the diagram of recommended user interface of 2QD0435T17xx-C-xx. There the diodes Dsox are only required when using 3.3V input logic level.

In a fault condition, the maximum SOx current must not exceed 20mA.

Figure 10. Block diagram and recommended circuit of status signal output

SO1 and SO2 can be connected together to provide protection information of the entire driver. However, for fast and precise fault diagnosis, it is recommended to detect the information independently.

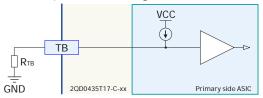

#### **Blocking Time Setting**

The blocking time  $t_B$  can be configured by an external resistor  $R_{TB}$  between TB pin and GND.

The following formula describes the relationship between  $t_B$  and  $R_{TB}$  (at typical values).

$$\begin{split} R_{TB}[k\Omega] = & t_B[ms] + 55 \\ (75k\Omega \leqslant R_{TB} \leqslant 185k\Omega, 20ms \leqslant t_B \leqslant 130ms) \end{split}$$

Note:  $R_{TB}$  should not be smaller than  $75k\Omega$ , which means the blocking time  $t_B$  cannot be shorter than 20ms, otherwise the blocking time  $t_B$  will be inaccurate and unstable. If TB pin is shorted to ground,  $t_B$  is fixed to 10us.

Figure 11. Blocking time setting

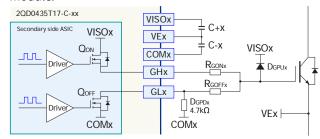

#### **IGBT Turn-On and Turn-Off**

To turn on the IGBT,  $Q_{ON}$  inside the ASIC of the driver is turned on, and  $Q_{OFF}$  is turned off. The gate resistor  $R_{GON}$  is pulled up to charge the gate and the IGBT is turned on.

To turn off the IGBT,  $Q_{OFF}$  inside the ASIC of the driver is turned on, and  $Q_{ON}$  is turned off. The gate resistor  $R_{GOFF}$  is pulled down to COMx to discharge the gate and the IGBT is turned off.

The driver allows user to set the turn-on and turn-off resistors independently. It is recommended to connect a resistor of  $4.7k\Omega$  between GLx and COMx. It is also recommended to add a clamping diode  $D_{GPUx}$ , which prevents overvoltages of the gate and protect the IGBT module.

Figure 12. Gate drive output circuitry

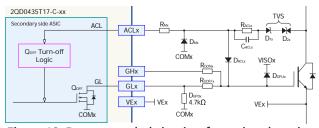

#### **Active Clamping**

Fast IGBT turn-off may lead to voltage spike, which is critical when DC-link voltage and load current are high. Voltage spikes can cause damage to the IGBT. The turn-off voltage spike is mainly due to the stray inductance Ls and the slew rate of the IGBT turn-off current di/dt. By adjusting the turn-off gate resistor RGOFF, the di/dt can be reduced and the voltage overshoot is reduced. However, the impact of Ls is inevitable. It can be more pronounced under high current in short circuit or overload. It is recommended to add active clamping circuitry to effectively prevent the overvoltage damage on IGBT.

A feedback path from the IGBT collector to the gate is established using transient voltage suppressor devices(TVS). When the  $V_{CE}$  peak voltage exceeds the breakdown threshold, the TVS chain will break through and the current through it will charge the IGBT gate, which turns on the IGBT partially and suppresses the excessive  $V_{CE}$  of the IGBT.

Anti-parallel diodes of the IGBT module have forward recovery effect when they are turned on, to avoid negative current flows through the TVS chain, at least one bidirectional TVS must be used for each channel.

The recommended breakdown thresholds for the application circuit of the driver are shown in the table below.

| DC Link<br>Voltage | TVS Chain<br>Breakdown<br>Threshold @ 25°C | D <sub>1x</sub> | D <sub>2x</sub> |

|--------------------|--------------------------------------------|-----------------|-----------------|

| 800V               | 912V                                       | 5 x SMBJ130A    | 1 x SMBJ130CA   |

| 1200V              | 1320V                                      | 5 x P6SMB220A   | 1 x PB6MB220CA  |

Figure 13. Recommended circuitry for active clamping

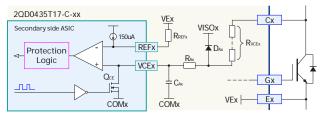

#### **IGBT Short-Circuit Protection**

The  $V_{\text{CE}}$  detection circuitry is used for IGBT short-circuit protection. The detection of two channels are independent from each other. The short-circuit detection

is only valid when the IGBT is turned on. When the IGBT is in off state, the input signal turns on  $Q_{\text{CEx}}$  and clamps VCEx to COMx. In this case, the comparator outputs logic low.

The threshold of comparator is set by external resistors  $R_{REFx}$  connected to  $R_{EFx}$  pin. Inside  $R_{EFx}$  pin there a built-in current source of 150uA, an external resistor  $R_{REFx}$  68k $\Omega$  configures a threshold voltage of 10.2V for the short circuit detection.

Figure 14. Block diagram and recommended circuit for short-circuit protection

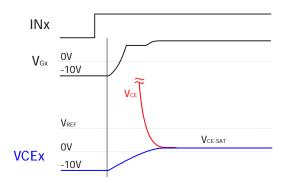

#### Normal Turn-on:

When the logic input will turn on the IGBT,  $Q_{CE}$  is firstly turned off and releases the clamping of VCEx clamping. At this moment, IGBT is still in off state and  $V_{CE}$  is high.  $C_{AX}$  capacitor is charged through the resistor chain composed of  $R_{VCEX}$  and  $R_{AX}$ , VCEx rises. Then the IGBT is turned on,  $V_{CE}$  quickly drops to saturation voltage  $V_{CE-SAT}$  and VCEx reaches  $V_{CE-SAT}$ .

The response time is the time interval between turnon of the IGBT and the collector voltage is started to be measured, within the response time,  $V_{CE}$  is deactivated. The response time can be determined by configuring the capacitor  $C_{Ax}$  following the table in below ( $R_{VCEx}$ =1.8M $\Omega$ ,  $R_{Ax}$ =120k $\Omega$ , DC link voltage >550V).

Table 1. Typical response time under different CAx and RREFX

| Cax [pF] | $R_{REFx}\left[k\Omega ight]/V_{REFx}\left[V ight]$ | Response time [μs] |

|----------|-----------------------------------------------------|--------------------|

| 15       | 68/10.2                                             | 6.1                |

| 22       | 68/10.2                                             | 7.5                |

| 33       | 68/10.2                                             | 9.4                |

| 47       | 68/10.2                                             | 11.6               |

Be sure to configure a response time that is shorter than the maximum allowed short-circuit duration of the IGBT. As  $V_{\text{CE-SAT}}$  is significantly lower than the protection threshold  $V_{\text{REF}}$ , the comparator does not flip over and the protection is not initiated.

Figure 15. VCEx signal waveform at normal turn-on

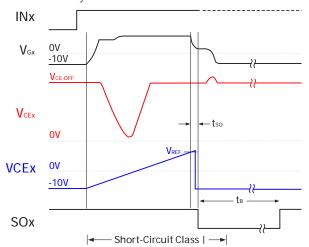

#### Class I Short- Circuit Protection:

When Class I short circuit (bridge shoot-through) occurs, due to the rapid increase of the short cirucit current, the IGBT desaturates and result in rapidly increased  $V_{CE}$ .  $C_{Ax}$  is charged and VCEx rises until it is clamped at VISOx. During this process, VCEx exceeds  $V_{REF}$  and the comparator's output flips, which consequently triggers the short-circuit protection.

The short-circuit protection logic turns off the IGBT immediately to ensure its safety. At the same time, set fault signal is sent to the primary side to pull down the SOx pin, so as to alert a fault state. The channel is locked in fault state for a period  $t_B$  before recovering to the normal state. The protection circuits of the two channels are independent from each other. Therefore, when short-circuit protection is initiated on one channel, the other channel remains operating normally. It is recommended to check the SOx signal timely and activate system lockout when necessary.

Figure 16. Logic of class I short-circuit protection

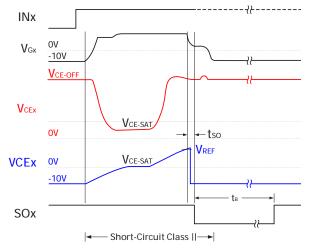

#### Class II Short-Circuit Protection:

When a Class II short circuit (e.g. phase to phase short circuit) occurs, the current ramps up slowly as the short circuit impedance is relatively high. The IGBT still enters saturation state normally. As the short-circuit current increases, VCE increases gradually until it exceeds the protection threshold, then the driver initiate short-circuit protection. The response time in Class II short-circuit protection is longer than that of Class I. In another case, if bridge shoot-through occurs under low DC-link voltage, the short circuit current is low and also resulting in increased protection response time.

Note: When a Class II short circuit occurs, the short circuit impedance varies greatly, which leads to uncertain timing of IGBT desaturation. Therefore, before the protection is initiated, the IGBT may have been already damaged by a considerable sum of heat accumulated. In this case, the driver's short-circuit protection cannot guarantee the intactness of the IGBT. Extra overcurrent protection measures have to be introduced.

Figure 17. Logic of class II short-circuit protection

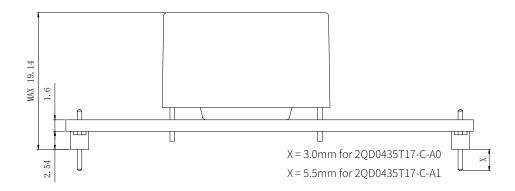

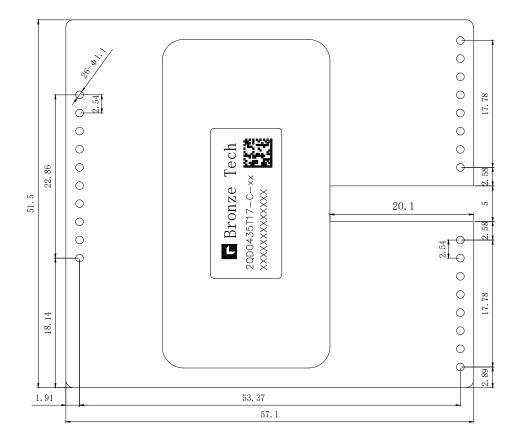

#### **Mechanical Dimensions**

Figure 18. Mechanical drawing of 2QD0435T17-C-xx

Note: 1)Legend unit: mm.

2) The margin tolerance conforms with the ISO 2768-1.

3)The primary side and secondary side pin grid is 2.54mm with a pin cross section of 0.64mmx0.64mm. Recommended diameter of solder pads is 2mm and diameter of drill holes is 1mm.

## **Revision History**

| REVISION | NOTES                                                      | DATE        |

|----------|------------------------------------------------------------|-------------|

| V1.0     | Initial release                                            | 12-Jun-2019 |

| V1.1     | Modified data                                              | 19-Jun-2019 |

| V1.2     | Updated introduction                                       | 20-Jul-2019 |

| V1.3     | Updated the manual template                                | 04-Nov-2019 |

| V1.4     | The manual template updated, and the content standardized  | 18-Aug-2021 |

| V1.5     | Content updated after introduction of 2nd generation ASIC  | 23-Sep-2023 |

| V1.6     | Updated figures and short circuit protection response time | 25-Dec-2023 |

#### **Precautions**

- All operations on the IGBT module and driver shall conform with the electrostatic-sensitive device (ESD) protection requirements stipulated in IEC 60747-1/IX or EN100015.

- To protect ESDs, IGBT module and driver operation, including the operation sites and tools, must conform with these standards.

#### The IGBT and driver may be damaged due to negligence in ESD protection.

- Before powering on the driver, make sure that the driver and control board are connected correctly, without empty connection, false connection, or false soldering.

- After the driver is installed, its surface voltage to the ground may exceed the safety voltage. Therefore, do not touch it with bare hands.

Operations may involve life hazards. Be sure to follow the corresponding safety protocols!

#### **DISCLAIMER**

The technologies and reliability data (including datasheets), design resources (including 3D models, structure diagrams, and AD models), application notes, application programs, and other design recommendations, tools, safety information and resources provided by Bronze Technologies do not constitute any guarantees, implicit or explicit, on the delivery, function, specific usage, applicability, or no infringement on a third party's intellectual property rights.

These resources are intended for engineers specialized in product development upon Bronze Technologies products, who are fully responsible for:

- 1) Choosing appropriate Bronze Technologies products for your products;

- 2) Design, verification, and testing of your products;

- 3) Ensuring that your products meet applicable requirements.

The data, documents, and resources are subject to regular updates without notification. Please visit BronzeTechnologies'website <a href="https://www.qtjtec.com">www.qtjtec.com</a> or WeChat official account for the latest resources.

You are authorized to use the resources only when you use the corresponding Bronze Technologies products, and however are prohibited from replicating or demonstrating these resources in other means. These resources do not constitute authorization of intellectual property rights of Bronze Technologies or a third party to any party.

Bronze Technologies assumes no liability in any claims, damages, losses, or costs incurred during your use of these resources and is entitled to recovery of losses caused by infringement of intellectual property rights.

#### Bronze Tech Group | Shenzhen Bronze Technologies Ltd.

Website: www.qtjtec.com Technical Support Tel.: +86 0755 33379866 Technical Support Email: support@qtjtec.com

Scan QR code to enter Bronze website.